-

Compteur de contenus

3 505 -

Inscription

-

Dernière visite

-

Jours gagnés

26

-

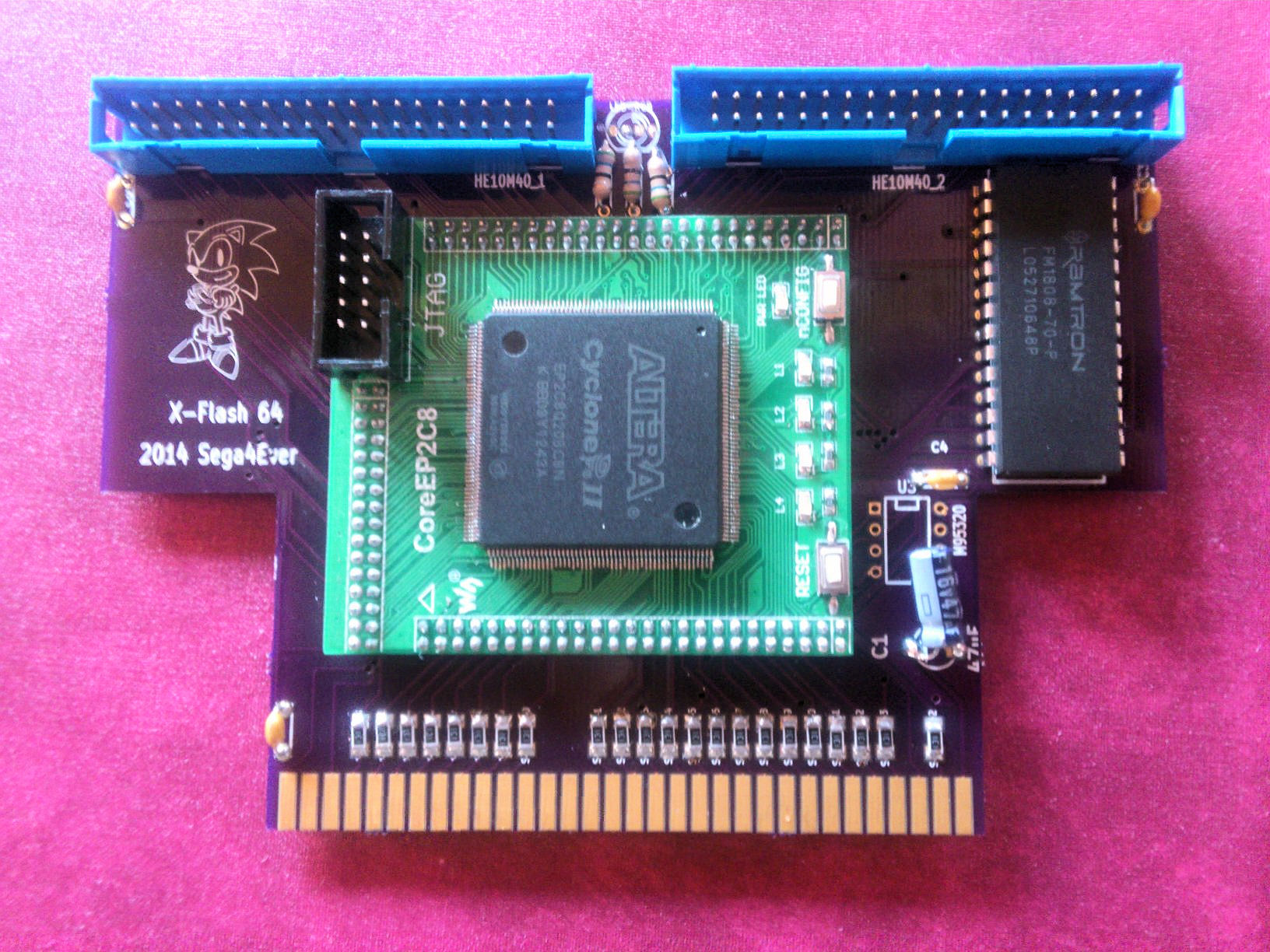

salut je suis limité a 3 message par jour pas evident de repondre ainsi (peu etre un bug ?) , donc pour resumer

power on ---> TMSS ---> ROM1

1er reset ---> ROM2

2eme reset ----> retour sur ROM1 bugg pas de son et/ou defaut de sprite

3eme reset ----> ROM2 bugg pas de son et/ou defaut de sprite

4eme reset ----> ROM1 sans bug ....ect